| Device Description | |

| HDMI Test Type | TMDS Physical Layer Tests |

| HDMI Specification | 2.0 |

| Test Session Details | |

| Infiniium SW Version | 04.50.0008 |

| Infiniium Model Number | DSOX93204A |

| Infiniium Serial Number | MY53180105 |

| Application SW Version | 1.99.9025 |

| Debug Mode Used | Yes |

| Probe (Channel 1) | Model: 1169A Serial: US44002033 Head: N5380A/B Atten: Not Calibrated, Using Default Atten (2.1036E+000) Skew: Not Calibrated, Using Default Skew |

| Probe (Channel 2) | Model: 1169A Serial: US48470614 Head: N5380A/B Atten: Not Calibrated, Using Default Atten (2.0989E+000) Skew: Not Calibrated, Using Default Skew |

| Probe (Channel 3) | Model: 1169A Serial: US44000715 Head: N5380A/B Atten: Not Calibrated, Using Default Atten (2.2949E+000) Skew: Not Calibrated, Using Default Skew |

| Probe (Channel 4) | Model: 1169A Serial: US44000259 Head: N5380A/B Atten: Not Calibrated, Using Default Atten (2.2029E+000) Skew: Not Calibrated, Using Default Skew |

| Last Test Date | 2013-09-09 09:42:31 UTC -07:00 |

| Margin Thresholds | |

| Warning | < 2 % |

| Critical | < 0 % |

| Pass | # Failed | # Trials | Test Name | Actual Value | Margin | Spec Range |

| 0 | 1 | 7-9: Clock Jitter | 229 mTbit | 8.4 % | VALUE <= 250 mTbit |

| 0 | 1 | 7-4: Clock Rise Time | 250.278 ps | 233.7 % | VALUE >= 75.000 ps |

| 0 | 1 | 7-4: Clock Fall Time | 261.922 ps | 249.2 % | VALUE >= 75.000 ps |

| 0 | 1 | 7-8: Clock Duty Cycle(Minimum) | 49.810 | 24.5 % | >=40% |

| 0 | 1 | 7-8: Clock Duty Cycle(Maximum) | 50.900 | 15.2 % | <=60% |

| 0 | 1 | 7-10: D0 Mask Test | 0.000 | 50.0 % | No Mask Failures |

| 0 | 1 | 7-10: D0 Data Jitter | 268 m | 10.7 % | <=0.3Tbit |

| 0 | 1 | 7-4: D0 Rise Time | 79.396 ps | 5.9 % | VALUE >= 75.000 ps |

| 0 | 1 | 7-4: D0 Fall Time | 75.740 ps | 1.0 % | VALUE >= 75.000 ps |

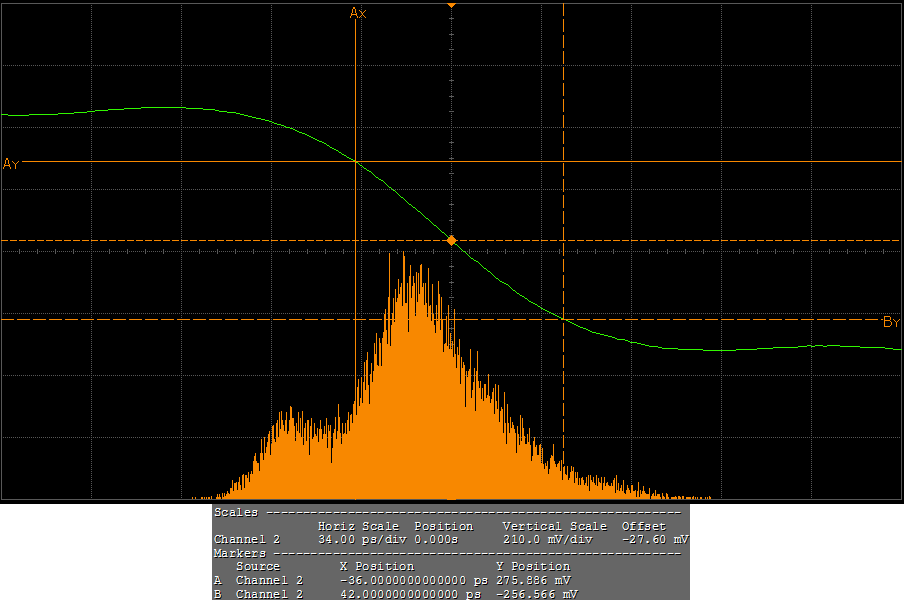

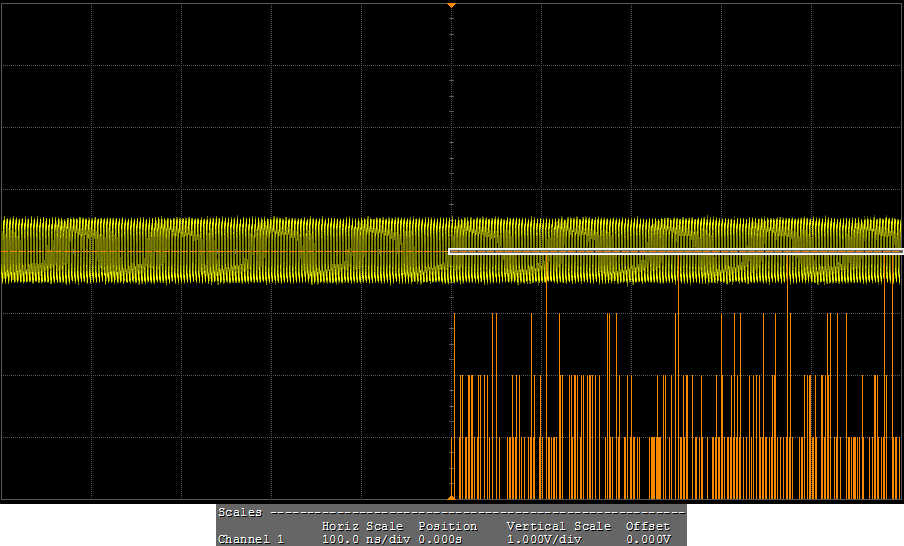

7-9: Clock Jitter

Reference:

Test ID 7-9

7-9: Clock Jitter

Reference:

Test ID 7-9

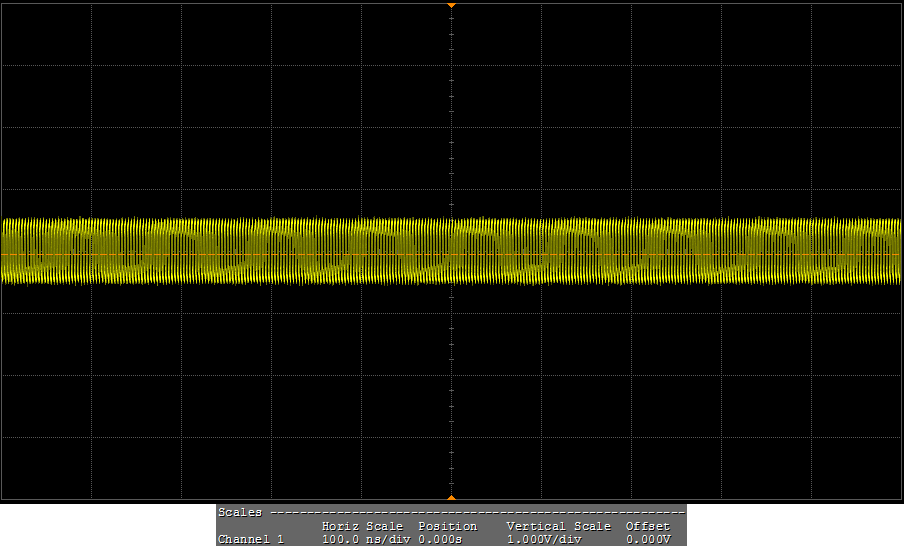

7-4: Clock Rise Time

Reference:

Test ID 7-4

7-4: Clock Rise Time

Reference:

Test ID 7-4

7-4: Clock Fall Time

Reference:

Test ID 7-4

7-4: Clock Fall Time

Reference:

Test ID 7-4

7-8: Clock Duty Cycle(Minimum)

Reference:

Test ID 7-8

7-8: Clock Duty Cycle(Minimum)

Reference:

Test ID 7-8

7-8: Clock Duty Cycle(Maximum)

Reference:

Test ID 7-8

7-8: Clock Duty Cycle(Maximum)

Reference:

Test ID 7-8

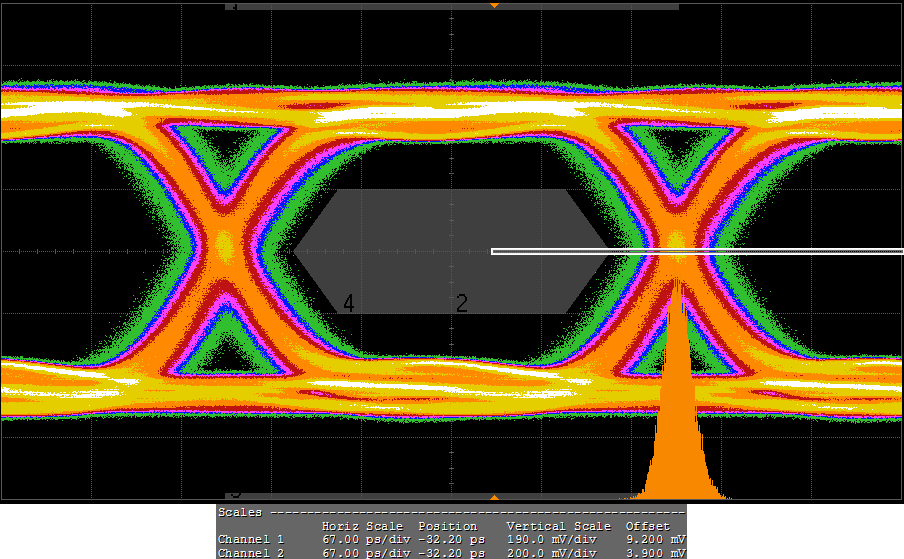

7-10: D0 Mask Test

Reference:

Test ID 7-10

7-10: D0 Mask Test

Reference:

Test ID 7-10

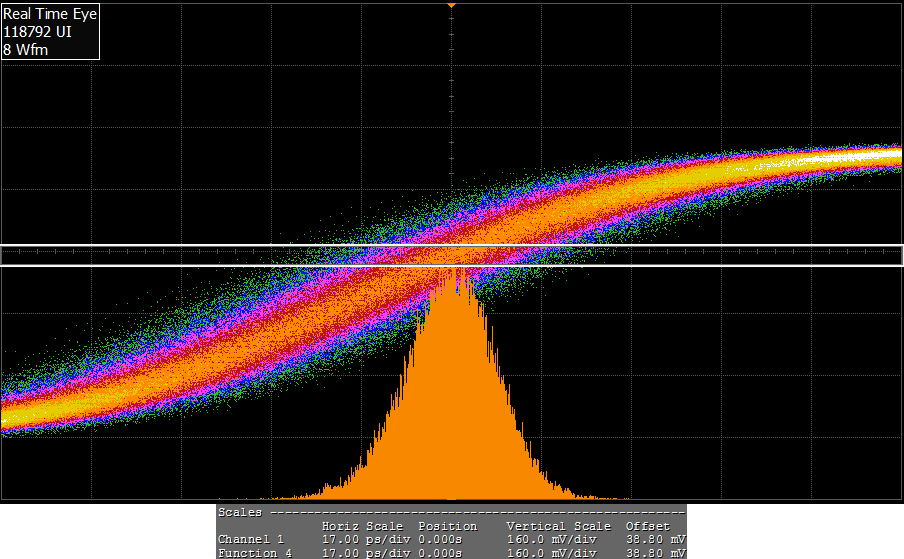

7-10: D0 Data Jitter

Reference:

Test ID 7-10

7-10: D0 Data Jitter

Reference:

Test ID 7-10

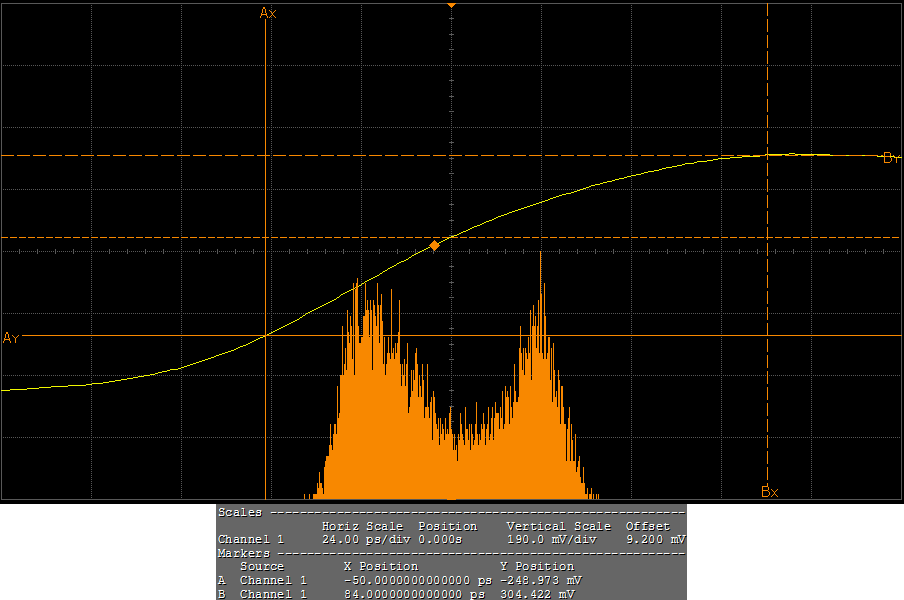

7-4: D0 Rise Time

Reference:

Test ID 7-4

7-4: D0 Rise Time

Reference:

Test ID 7-4

7-4: D0 Fall Time

Reference:

Test ID 7-4

7-4: D0 Fall Time

Reference:

Test ID 7-4